做小尺寸工业屏项目,最容易被低估的一件事就是“接口选择”。很多人拿到需求,第一反应是先定一块液晶屏或LCD液晶屏,再去适配主控;结果到联调阶段才发现:要么SPI刷新慢、画面拖影;要么MIPI走线苛刻、EMI和结构空间过不了;要么面板缺货换型,液晶屏接口直接把整机推倒重来。

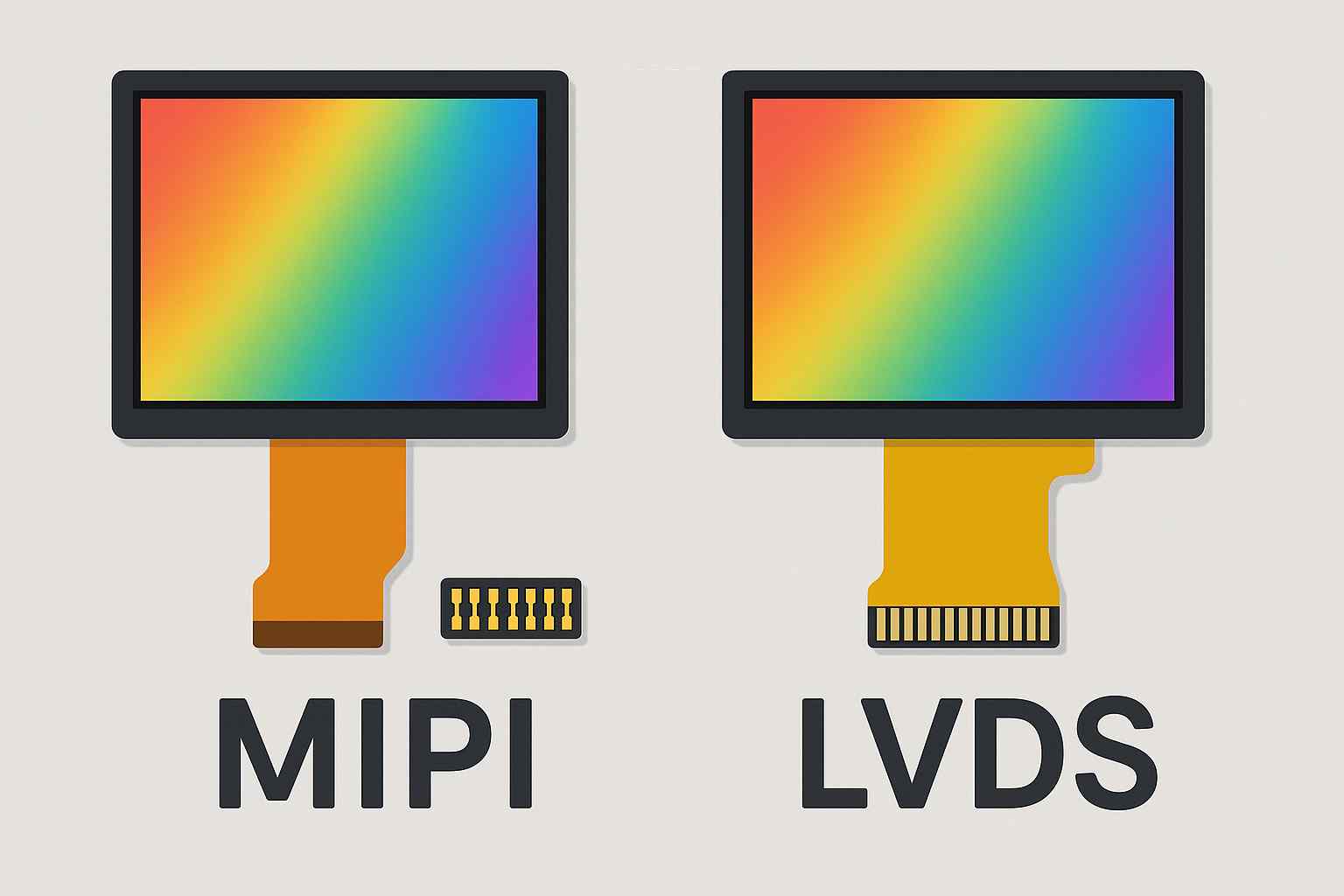

MIPI(通常指MIPIDSI)与SPI都能驱动小尺寸液晶屏/工业液晶屏,但它们在带宽、时序方式、硬件复杂度、可维护性和供应链策略上完全不是一个物种。立煌按“工程选型”的口径讲清差异,并给出小尺寸工业屏(常见1.3–10.1英寸)在不同场景下的选择建议。

一、MIPI这里通常指MIPI DSI

在显示领域说“MIPI屏”,多数指MIPIDSI作为液晶屏接口,由主控通过D-PHY/C-PHY把像素数据以高速串行方式送到显示端。DSI常见两种传输形态:VideoMode(视频流模式)与CommandMode(命令模式),前者更像持续“推流”,后者更像按需写显存。命令/视频两种模式是DSI体系内的重要差异点,很多SoC/MCU只支持其中一种,直接影响你能否用MIPI屏落地。

SPI(SerialPeripheralInterface)则是更通用的同步串行外设总线,常见4线(SCLK/MOSI/MISO/CS)或3线模式。把SPI用作液晶屏接口时,本质是主控通过SPI向显示控制器/驱动IC写命令和像素数据,属于“通用总线驱屏”。

二、最核心的差异:

带宽数量级不同,决定了“屏能不能像你想的那样动起来”

1、MIPI DSI的带宽上限:

按“每条lane的Gbps”计,MIPI DSI底层常用MIPID-PHY。公开资料中对D-PHY不同版本的演进给出了典型数据速率:例如D-PHY1.1约1.5Gbps、1.2约2.5Gbps、2.1约4.5Gbps(每lane速率随版本提升)。

这意味着:即便是相对常见的“4lane、每lane1.5Gbps”的组合,理论吞吐也已达6Gbps量级(再扣除协议开销和编码/空白区,仍远高于SPI)。

同时,MIPI对走线/损耗的要求也会随速率提高而显著收紧;例如在路由约束文档中,会将不同速率下的走线长度、损耗等约束写得非常具体,工程实现的难度与成本需要提前算进去。

2、SPI的带宽上限:

按“几十MHz~几十Mbps”计(且受系统约束很大)SPI本身不是为视频流设计的。即使在一些控制器/MCU模块资料里,SPI数据率也常见在几十Mb/s量级,例如某些SPIMaster组件给出“数据率到33Mb/s”的能力描述。

而显示驱动IC侧往往还有自己的时序上限。以常见小屏驱动ICST7789为例,有资料依据其数据手册给出“最小SPI时钟周期16ns,对应最高约62.5MHz”的推导(实际项目还会受线长、EMI、主控能力、DMA效率影响而低得多)。

更重要的是:不少现成SPI液晶模组为了兼容更广的主控和更长排线,甚至会把SPI时钟限制得更保守(例如某些模组手册给出最大8MHz的建议值),这会把刷新率进一步压低。

三、工业液晶屏到底需要多大带宽?

决定液晶屏接口是否够用,最简单的方法是把“你要的画面”换算成码率需求:

码率(bit/s)≈分辨率(W×H)×刷新率(fps)×每像素位数(bpp)(若要更严谨,再加上行/场消隐、协议开销、总线效率等折损。)

示例A:480×800、60Hz、RGB565(16bpp)

码率≈480×800×60×16=368,640,000bit/s≈369Mb/s

这还是“净像素数据”,没算额外开销。

结论很直观:单线SPI就算跑到62.5MHz(≈62.5Mb/s)也远远不够,哪怕你降低刷新率到20Hz,仍会非常吃力,且CPU/DMA占用高、整机响应变差。相反,MIPIDSI在lane级Gbps吞吐下处理这类分辨率会轻松很多。

示例B:240×240、20Hz、RGB565(16bpp)

码率≈240×240×20×16=18,432,000bit/s≈18.4Mb/s

这类“低分辨率+低刷新+UI为主”的液晶屏场景,SPI就很常见:配合DMA、区域刷新、脏矩形更新,体验可以做到“够用且省成本”。

这也是小尺寸工业屏选型的分水岭:

1·你要的是“流畅动画/视频/相机画面/高帧率曲线”?MIPI更像正解。

2·你要的是“静态UI+少量局部刷新+低功耗+简单主控”?SPI往往更划算。

四、MIPI DSIvsSPI:

1、数据传输形态:推流vs写数据

MIPIDSIVideoMode:持续输出像素流,更像显示管线的一部分;

MIPIDSICommandMode:按命令写入显示端缓存/GRAM,适合局部更新与省电策略。

SPI:几乎总是“写命令+写像素”,你刷新多少,就传多少;没有天然的视频管线优势。

2、主控门槛:不是“想用就能用”

MIPI需要主控端有DSIHost与PHY资源(很多MCU没有,部分新MCU/SoC才逐步具备);并且你的软件栈需要驱动DSI、时序、面板初始化、背光与电源序列等。

SPI基本任何MCU/MPU都能上,驱动成熟、联调简单,是“低门槛液晶屏接口”。

3、走线与EMI:MIPI更苛刻但更“体系化”

MIPID-PHY属于高速差分链路,对阻抗控制、走线长度、损耗、连接器与排线都有更明确的工程约束;速率越高,约束越严。

SPI在低速时对走线不敏感,但你一旦把SPI拉到几十MHz,长线、地弹、串扰也会迅速引出花屏/误码;更现实的是,很多模组会建议把SPI时钟限制在较低水平来换取稳定。

4、功耗:取决于“你怎么刷新”

MIPIVideoMode持续推流,适合高刷新,但在“长期满帧刷新”的场景功耗会更稳定且可预期。

SPI如果你一直全屏刷,主控和总线负载都高;但如果你只做局部刷新,SPI反而能把功耗做得很低。

因此功耗不是简单“谁更省”,而是与你的UI刷新策略强相关。

5、可维护性与返修:SPI更友好

SPI模组通常封装简单、替换容易;MIPI屏常牵涉更严格的时序、供电序列、背光与复位控制,且一旦换屏(尤其跨厂/跨驱动IC),软件适配成本更高。对“工业液晶屏长期供货”而言,你需要更早规划替代料策略。

6、MIPI更偏手机/消费链路,SPI更偏嵌入式/通用模组

小尺寸LCD液晶屏里,MIPI屏的规格、排线、初始化序列往往更依赖具体面板与厂商生态;SPI屏(如常见控制器系列)在嵌入式生态里普及度更高,资料与开源驱动更多,二供/三供也更容易做备选。

7、显示效果上限

当你需要高分辨率、高刷新、高色深时,SPI很快会碰到物理上限;MIPI能给你的上限更高,这就是为什么手机屏、车载中控、高清小屏大量采用MIPIDSI。

8、系统成本

MIPI线束少、引脚少看似“省”,但PHY、PCB工艺、调试成本、合格率、EMI整改等隐性成本往往更高;SPI引脚多一些,但方案轻、便于快速量产。对小尺寸工业液晶屏项目来说,“总体成本”要算全生命周期,而不是只算连接器针脚数。

五、小尺寸工业屏怎么选

下面用最常见的工程分类来给选择建议,便于你写进官网或内部选型规范。

场景1:静态信息为主

特征:刷新区域小、帧率要求低、主控多为MCU、追求稳定与成本。

建议:优先SPI(或并口8080/6800一类,但本文聚焦SPI)

关键落地点:

用DMA+局部刷新(脏矩形)减少总线占用

把SPI时钟设在“稳定优先”的区间,别盲目追求峰值(很多模组/系统在高频下会不稳定)

UI设计上避免全屏高频动画,换取更稳的工业体验

场景2:动态图形较多

特征:需要更高吞吐,SPI全屏刷新容易卡顿。

建议:优先MIPIDSI(或至少预留升级到MIPI的路线)

关键落地点:

明确主控是否支持所需DSI模式(Video/Command);很多平台支持情况不同

早期把PCB走线、连接器与排线方案按高速链路标准设计,避免后期返工

场景3:高分辨率小屏

特征:带宽需求直接上百Mb/s甚至更高。

建议:基本锁定MIPIDSI

原因:用前面的带宽估算你会发现,SPI很难在合理功耗与CPU占用下达到可用刷新。MIPID-PHY的lane级Gbps能力就是为这类数据量设计的。

场景4:极端强调可靠性

特征:线缆更长、环境噪声大、维护要求高。

建议:不要只在“MIPIvsSPI”里二选一

工程上常见做法是:

如果必须长距离,考虑把显示链路做“桥接/转换/分布式”(例如DSI转eDP/LVDS再走更适合的链路,或干脆显示端本地渲染)

若仍走SPI,宁可降速换稳定,并用更好的屏蔽与接地策略;若走MIPI,则更要严格遵循高速链路的长度与损耗约束

六、把“接口选择”写进需求单:

为了避免选型反复,建议你在需求单里把以下信息固化(官网也可以用作“咨询表单引导”):

1、目标分辨率与期望刷新体验(静态/20Hz/60Hz/动画多不多)

2、色深(RGB565还是RGB888等)与显示内容类型(UI/视频/相机)

3、主控平台(MCU/MPU/SoC)及是否具备MIPIDSIHost能力

4、结构与线缆形态(板对板/FFC长度/连接器类型/是否分体)

5、EMI环境与可靠性要求(变频器、电机、静电、强电共地等)

6、供应链策略(是否需要二供、生命周期、替代料准备)

这些信息一旦齐全,“液晶屏接口选MIPI还是SPI”通常不再是争论题,而是一个可以推导的结论。

七、常见问题

Q1:小尺寸工业液晶屏用SPI一定会卡吗?有没有办法“看起来很流畅”?

不一定。SPI的瓶颈主要在带宽,若你是低分辨率、低刷新、以静态UI为主的应用,通过“局部刷新(脏矩形)+DMA+降低全屏刷新频率”,体验可以做到很顺滑。真正容易卡的是:高分辨率还要全屏高帧率动画/视频,这种需求本质就更适合MIPI一类高速显示接口。

Q2:MIPIDSI的VideoMode和CommandMode怎么选?

如果你要持续高帧率、画面像视频流一样稳定输出,通常更偏VideoMode;如果你更多是界面交互、局部更新,希望减少不必要的全屏推流和功耗,CommandMode更常见。但最终要以主控平台对DSI模式的支持情况为准,有些平台只支持其中一种,选屏前必须确认驱动与时序能落地。

Q3:MIPI屏为什么更容易遇到花屏、白屏、偶发闪烁?

常见原因是高速差分链路对走线、阻抗、长度匹配、连接器与排线质量更敏感。尤其当速率提高或FFC线变长时,信号裕量被压缩,偶发误码就会表现为花屏或闪烁。工程上通常需要更严格的PCB布线规范、合适的连接器/线材、以及必要的EMI与信号完整性验证。

Q4:SPI时钟我能不能直接拉到很高来“硬刷帧率”?

理论上部分控制器/主控能支持更高SPI频率,但实际项目往往会受限于线长、地弹、串扰、模组建议时钟、DMA效率和CPU占用。频率拉得过高,可能出现随机花点、撕裂、偶发掉帧,甚至在批量一致性上翻车。更稳的做法是:先把刷新策略改成局部更新,再在“稳定优先”的频率区间内优化性能。

Q5:小尺寸工业屏除了MIPI和SPI,还有没有更合适的接口?

有。很多工业液晶屏/液晶模组还会用并口8080/6800、LVDS、eDP等方案:并口在中等分辨率下能提供更高吞吐但占用IO多;LVDS/eDP更偏中大尺寸或特定平台。选接口时最关键的是:主控资源、目标分辨率/帧率、线缆形态与EMI环境。不要把自己锁死在“MIPIvsSPI”二选一里。

八、先定画面目标再选链路

MIPI与SPI的核心差异不是“谁更高级”,而是它们服务的画面目标不同:

1·要高分辨率、高刷新、视频流与更强显示上限,MIPI DSI(配合D-PHY的Gbps级吞吐)更符合体系设计初衷。

2·要低功耗、低成本、静态UI为主、快速量产与易维护,SPI依旧是小尺寸工业液晶屏非常现实且成熟的选择,但要接受它在带宽上的天花板,并用“局部刷新+稳定时钟”把体验做稳。

杭州立煌科技有限公司作为一家专注于工业领域的液晶显示驱动方案提供商,与京东方(BOE)、天马(TIANMA)、龙腾(IVO)、友达(AUO)、群创(Innolux)、京瓷(Kyocera)等多家全球领先液晶面板制造商建立深度合作关系,专业供应多品牌、全系列的工业级液晶显示屏与定制化解决方案。

服务热线:

服务热线: