很多7寸1024×600项目翻车,不是因为屏不好、主板不好,而是因为大家用“消费电子的直觉”在做“工业配套”:

拿到液晶屏先问接口,拿到主板先问有没有LVDS,然后凭“看起来差不多”就下单。结果样机能亮,量产花屏;维修换屏,分辨率一样却黑屏;或者更隐蔽:能亮但颜色不对、灰阶断层、偶发闪屏。

1.配主板不是“配接口”

配主板不是“配接口”,而是配一条“显示链路契约”,7寸1024×600只是“像素数量”。主板能不能带起来,取决于你能不能把以下契约对齐:

1.主控输出的显示接口类型(RGB并口/LVDS/eDP/MIPIDSI/HDMI通过转换)

2.像素位宽(bpp)与色彩格式(18-bit/24-bit,JEIDA/VESA,RGB565/RGB666/RGB888等)

3.时序模型(DE模式还是HS/VS模式、极性、像素时钟、前后肩)

4.电源与背光(屏端3.3V/5V/12V,背光是否需要外置恒流、PWM频率范围)

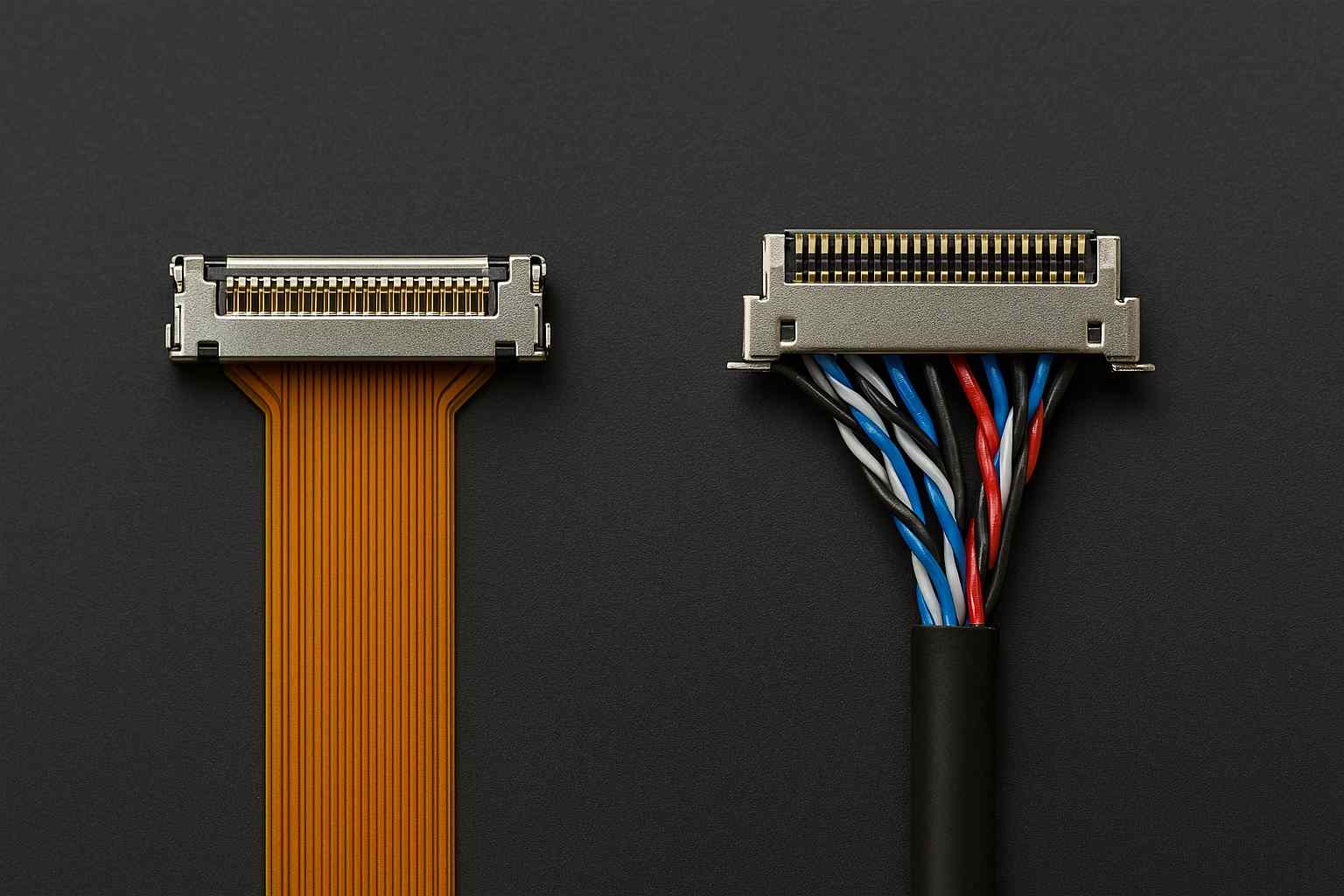

5.物理连接与抗干扰(连接器型号、线束长度、屏蔽与接地、EMI/ESD)

只要其中任何一项没对齐,都会出现你熟悉的“花屏/闪屏/白屏/颜色不对/偶发不亮”。

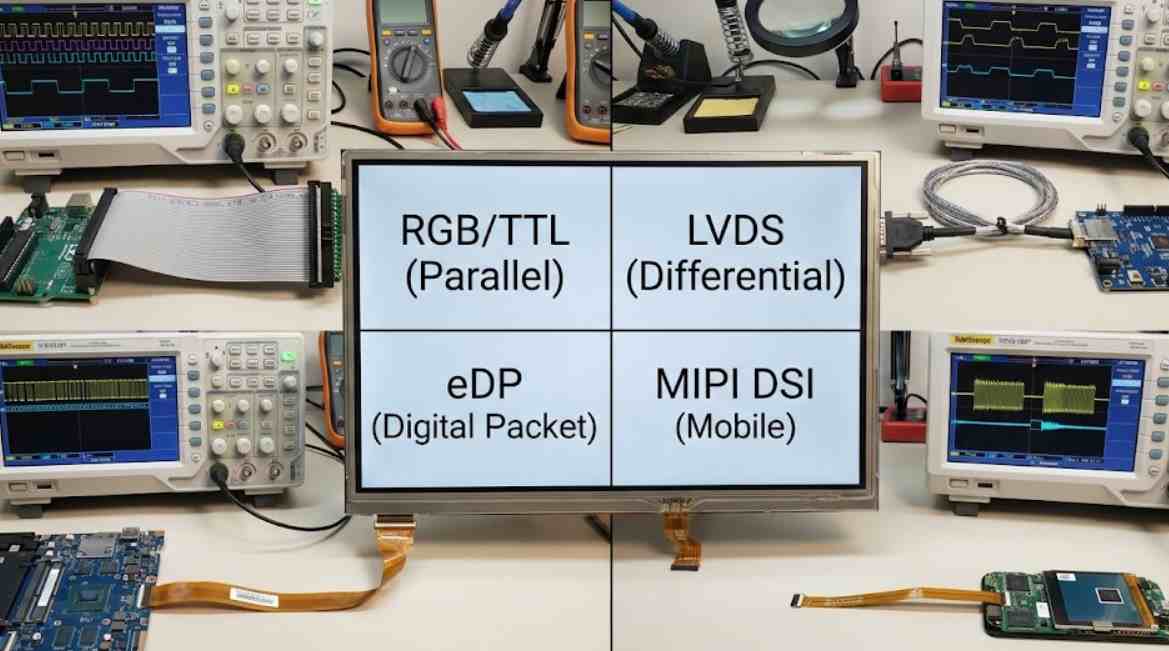

2.7寸1024×600常见接口有哪几类?

同样是1024×600,市场上可以出现多种接口形态,最常见是这三类:

2.1LVDS

(最常见的“工控屏”路径)

很多7寸与10.1寸工业模组会提供LVDS版本,例如Winstar的1024×600LVDS模组就明确标注LVDSinterface。

LVDS的优势是抗干扰相对好、线束可更长、工业应用成熟;但它的“坑”集中在:映射(JEIDA/VESA)、位宽(18/24)、单/双路、通道极性。

TI的LVDS映射应用笔记明确讨论了JEIDA与VESA的数据映射,并指出JEIDA对24→18bit切换更方便。

2.2RGB并口

(DPI/TTL/CMOS,常见于小尺寸与某些工控板)

有些1024×600模组提供RGB24-bit接口(通常用于MCU/SoC直接并口输出)。比如有供应商公开页就写到1024×600、RGB_24bitinterface的模组。

RGB并口的核心特点:线多、单端高速、对线束长度非常敏感。主板上有并口不等于你能把屏拉到很远的前面板位置。

NXP的应用笔记也直接指出:传统并口24bpp会需要24根数据线外加VSYNC/HSYNC/DE/CLK等控制线。

2.3MIPIDSI

(在ARMSoC、平板/工控一体机上越来越常见)

MIPIDSI的“位宽”并不是靠增加线数实现,而是靠高速串行链路传输;它定义了不同像素格式(18-bit/24-bit)对应的数据类型(DataType)与封装方式。MIPIDSI规范里就列出了18-bit与24-bit的像素流封包条目。

TI的DSIbringupguide也把RGB888(24-bit)、RGB666(18-bit)等模式写得很明确。

现实建议:

如果你的主板原生就是MIPIDSI,尽量选同为MIPI DSI的工控液晶屏;

如果屏是LVDS,而主板是MIPIDSI/HDMI/eDP,别硬接,走“桥接/SerDes”路线更可控(后面会讲边界)。

3.“位宽”到底在核对什么?

很多人把位宽当成“颜色位数”,问完就结束。真正要核对的是三个层面:

3.1屏端“输入位宽”vs面板“内部显示色深”

屏端接口可能是18-bit(RGB666),但面板内部通过抖动/算法也可能看起来接近24-bit;反过来也一样。对配板来说,关键是“输入接口期望的位宽”。

3.2LVDS位宽不仅是“18/24”

同样24-bitLVDS,JEIDA与VESA的打包/映射不同。TI的映射文档就是专门解决这类互操作问题的。

这也是为什么“同为LVDS也可能不通”,甚至“能亮但颜色怪”。

你如果用过TI的LVDSserializer(例如DS90C185),它就明确支持两种模式:24-bit与18-bitRGB。

这意味着:你的链路上只要有一个环节(主板输出、桥接芯片、屏端接收)模式不一致,就会出事。

3.3MIPI DSI位宽是“像素格式”:RGB565/666/888

MIPI DSI位宽是“像素格式”:RGB565/666/888,MIPIDSI里,18-bit与24-bit对应不同的数据类型/封包方式(例如RGB666、RGB888)。

所以不能只问“DSI几lane”,还要问“DSI发的是什么像素格式”。

4.接口与位宽核对方法

下面是立煌建议你在内部或与供应商沟通时使用的“核对卡片”。它比“问一堆零散参数”更省事,也更不容易漏项。

卡片A:主板输出能力

1.输出接口:LVDS/RGB并口/MIPIDSI/eDP/HDMI

2.LVDS的话:单路/双路、JEIDA或VESA、18/24-bit、像素时钟范围

-这类项在TI的AM62PLVDS集成文档里就明确列为配置项:maptype(VESA/JEIDA、18/24)与inputbitwidth。

3.DSI的话:lane数、最大速率、支持的像素格式(RGB565/666/888)

4.RGB并口:支持18bit还是24bit,是否支持DE模式,像素时钟上限

卡片B:屏端接口期望

1.接口类型(不要只写“LVDS”,要写“single/dual、JEIDA/VESA、18/24”)

2.输入电源(3.3V/5V/12V)与背光供电

3.是否需要背光恒流驱动,PWM频率/电平要求

4.连接器:型号、pin定义、线束方向(别只看针数)

卡片C:位宽一致性判定

1·主板24-bit→屏24-bit:最理想

2·主板24-bit→屏18-bit:可行,但要确认LSB丢弃的映射方式(LVDSJEIDA切换特别常见)

3·主板18-bit→屏24-bit:多数情况下不建议,除非屏/桥接明确支持padding或重复填充

4·DSIRGB888→屏端期望RGB666:会导致颜色/时序异常(必须一致)

卡片D:时序与极性核对

1·分辨率只是activearea,真正决定稳定的是:

a.像素时钟(PCLK)

b.水平总周期(active+porch+sync)

c.垂直总周期

d.HS/VS/DE极性

2·对LVDS来说,还要核对“单像素/双像素每时钟”与通道映射(双路LVDS经常按奇偶像素分配)

这一步你不一定要背数值,但你要养成“拿到屏参数→写成主板可配置项→对齐”的习惯。

5.常见“配错主板”的3类场景:

场景1:主板是LVDS,屏也是LVDS

主板是LVDS,屏也是LVDS——最容易,但也最容易“颜色不对”,要做的不是“确认有LVDS”,而是确认:

1·18/24-bit

2·JEIDA/VESA映射

3·单/双路

TI的映射与互操作文档正是解决JEIDA/VESA映射差异的。

典型现象:

-能亮但偏色、灰阶怪→常见是JEIDA/VESA或位宽映射问题

-偶发闪屏→常见是时序边界、线束反射、供电纹波

场景2:主板是MIPIDSI,屏是LVDS

主板是MIPIDSI,屏是LVDS——不要硬转“几根线”,走桥接/SerDes,DSI是串行协议,LVDS是差分并行映射,两者不是简单换线。你通常需要:

2·DSI→LVDSbridge,或

2·DSISerDes+解串到LVDS(车载/长线束常用思路)

在DSI世界里,你必须对齐像素格式(RGB888/666等)。如果对齐了格式,桥接才有意义。

场景3:主板只有HDMI/eDP,屏是LVDS

eDP/DP体系有链路训练(LinkTraining)等机制,跟LVDS的固定映射不同;VESA对DisplayPort的技术概览中就提到链路训练会在初始运行或错误后重新发起。

这类场景通常用成熟的HDMI/eDP→LVDS控制板(带EDID、时序配置)会更稳,但成本与验证周期也更高。

只要出现“协议不一致”,就不要用“线材思维”,要用“系统思维”。

6.线束与抗干扰:

7寸屏配主板,很多问题其实是“线”而不是“屏/板”

6.1RGB并口:能短就短

NXP的描述已经揭示了并口的天生劣势:线太多。

并口拉长后常见问题:串扰、地回流不连续、时序偏斜,最终表现为花屏/抖动。

6.2LVDS:不是“随便一根排线”就行

LVDS虽然抗干扰好,但你仍要注意:

1·屏蔽与参考地

2·线对一致性

3·连接器与线束压接工艺

更重要的是:先把JEIDA/VESA、18/24-bit配置对齐,否则线再好也白搭。

6.3MIPIDSI:

lane数/速率/格式对齐后,才谈物理实现

DSI规范明确了不同像素格式封包条目,格式不一致时你看到的不是“有点差”,而是“根本不对”。

7.把“核对方法”落地成一个可执行流程

你可以按这个顺序推进项目,基本能把80%的返工风险挡在前面:

1.明确场景需求:室内/户外、是否触控、线束距离、温度范围、寿命目标

2.先定接口路线:优先用主板原生接口匹配屏(LVDS配LVDS、DSI配DSI)

3.锁定位宽与格式:LVDS18/24+JEIDA/VESA;DSIRGB565/666/888

4.核对连接器与pin定义:针数一致不等于兼容

5.核对时序参数:PCLK、porch、极性、DE/HSVS模式

6.背光与供电评审:供电余量、PWM频率、电源纹波

7.做两类验证:

1·功能验证:点亮、颜色、触控(如有)

2·压力验证:满亮运行、高温/低温、长线束、强干扰环境

8.常见问题

Q1:同样是7寸1024×600,为什么有的屏是LVDS有的是RGB?

A:因为分辨率不决定接口,接口取决于屏厂的驱动架构与目标平台。LVDS更偏工控与中长线束,RGB并口更偏SoC近距离直连;DSI则常见于移动/ARM平台。

Q2:我主板写“支持LVDS”,是不是随便找个LVDS屏都能用?

A:不是。至少要核对18/24-bit与JEIDA/VESA映射。TI的互操作文档就是专门解决“同为LVDS仍不兼容”的问题。

Q3:18-bit和24-bit的差异,实际肉眼能看出来吗?

A:很多UI下不明显,但在渐变灰阶、暗部细节、彩色过渡时更容易出现“断层”。更关键的是:配错位宽往往不是“变差一点”,而是“颜色异常/不稳定”。DSI与LVDS都明确把18/24当作不同模式处理。

Q4:主板是MIPIDSI,能不能用转接线接LVDS屏?

A:不能用“转接线思维”。需要桥接/SerDes等协议转换,并且要对齐DSI的像素格式(RGB888/666等)。

Q5:样机点亮了,是不是就可以量产?

A:不够。你至少要做满亮运行、温度压力、线束批次一致性与干扰场景验证。工业问题常在边界条件出现:供电余量、EMI、线束工艺、格式映射。

服务热线:

服务热线: